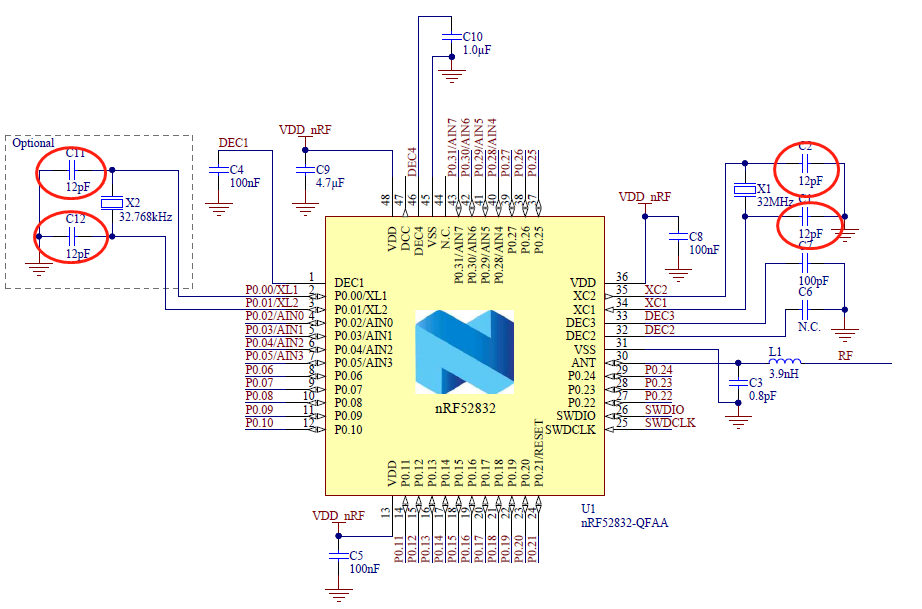

ЦЪЛщЦЬЦЄЈ¬Nordic Semiconductor nRF52ПµБРµДНвІї32MHZёЯЖµѕ§ХсєН32KHZµНЖµѕ§ХсЈ¬¶јРиТЄјУЖҐЕдµзИЭАґ±ЈЦ¤К±ЦУѕ§МеµДѕ«¶ИЎЈХвСщЧцµД±Ч¶ЛКЗФцјУБЛBOMіЙ±ѕЈ¬ёьЦШТЄµДКЗФцјУБЛїЄ·ўєНІвКФµДёґФУРФЈ¬їН»§НщНщІ»ЦЄµАЧФјєСЎУГµДѕ§ХсЈ¬У¦ёГЖҐЕд¶аЙЩpfµДµзИЭЈ¬УИЖдКЗ32MHZѕ§ХсЈ¬ОЄБЛИ·±ЈУРєЬєГµДЙдЖµМШРФЈ¬РиТЄѕЎїЙДЬµДјхЙЩЖµЖ«Ј¬ґЛК±РиТЄУГЖµЖЧТЗІвБїЙдЖµµДЖµЖ«Ј¬ФЩёщѕЭІвКФЅб№ыµчХыЖҐЕдµДµзИЭЈ¬·ЗіЈєД·СК±јдЎЈ

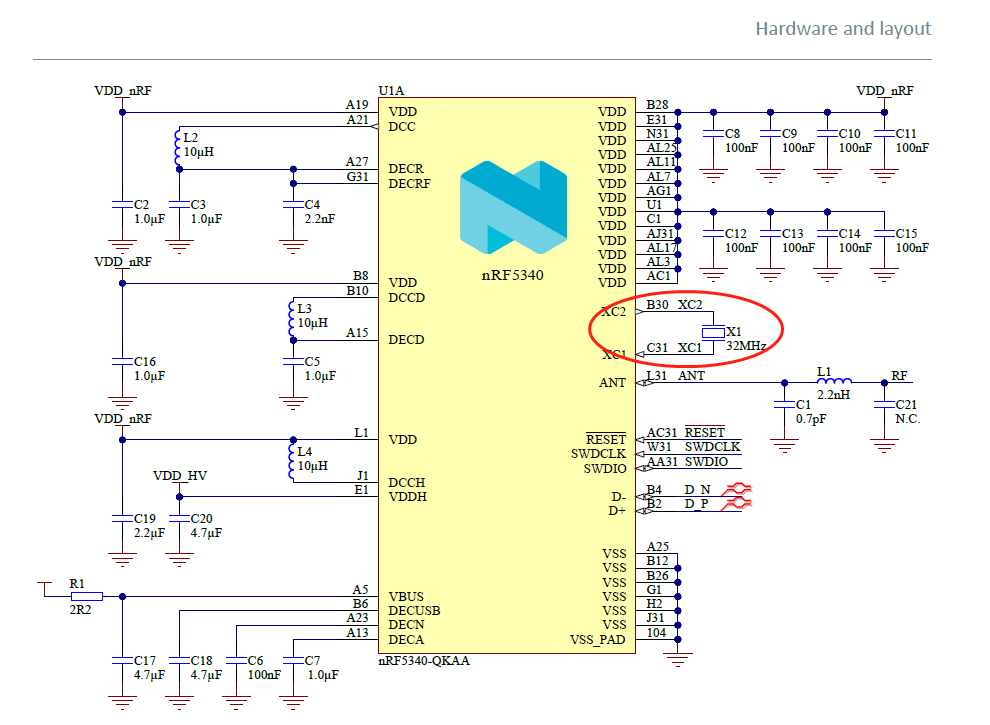

µЅБЛnRF5340Ј¬ОТГЗФЪІОїјµзВ·ЙијЖЙПЦ±ЅУКЎµфБЛХвЛДёцНвІїµзИЭЈ¬ІЙУГРѕЖ¬ДЪЦГµзИЭµД·ЅКЅЈ¬НвІїѕ§ХсЦ±ЅУЅУРѕЖ¬µДТэЅЕЈ¬ХвСщЧцјхЙЩБЛBOMіЙ±ѕєНїЄ·ўІвКФµДёґФУ¶ИЈ¬їН»§І»РиТЄїјВЗИзєОµчКФЖҐЕдµзИЭЎЈ

µ«КЗЈ¬К№УГnRF5340РѕЖ¬µДДЪЦГµзИЭЈ¬ТІУРТ»Р©РиТЄЧўТвµДµШ·ЅЎЈ

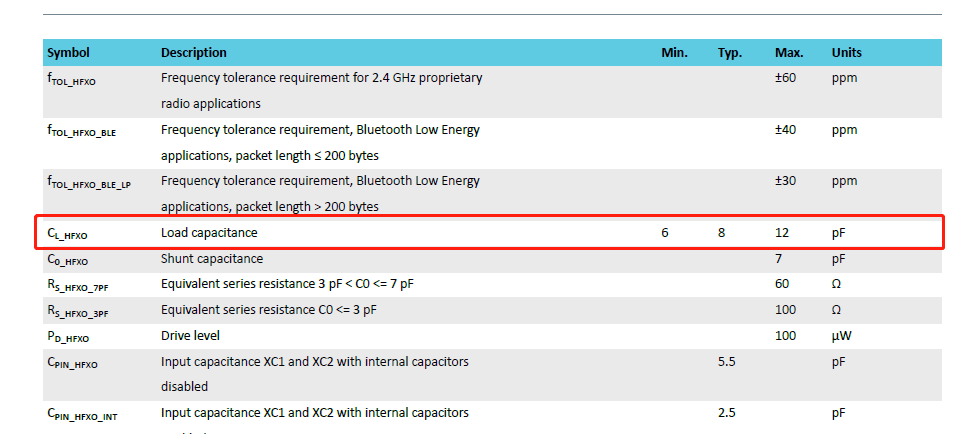

1.СЎУГµДНвІїёЯЖµѕ§ХсєНµНЖµѕ§ХсµДёєФШµзИЭCLРиТЄВъЧгnRF5340РѕЖ¬КЦІбЦР№ж¶ЁµД·¶О§Јє

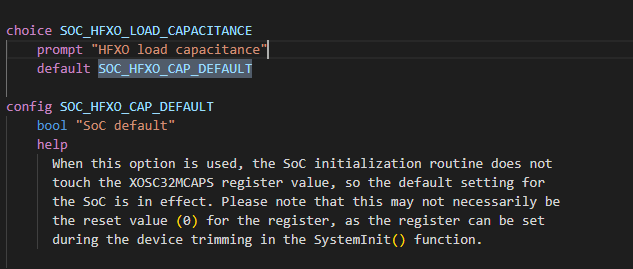

2.nRF5340РѕЖ¬µДіці§Д¬ИПК№УГµДКЗДЪІїµзИЭЈЁУЙРѕЖ¬ДЪІїПа№ШјДґжЖчµДИ±КЎЦµѕц¶ЁЈ©Ј¬NCSЦРД¬ИПµДЕдЦГОЄCONFIG_SOC_HFXO_CAP_DEFAULT=y,УЙґЛKconfigµДЧўКНЦРїЙТФµГЦЄЈ¬NCSЦРІЙУГµДКЗРѕЖ¬іці§К±јДґжЖчЦРµДЦµЈє

ФЪРѕЖ¬КЦІбЦРїЙТФІйµЅЈ¬ёЯЖµѕ§ХсµДДЪІїЖҐЕдµзИЭµДјЖЛ㹫ʽИзПВЈє

CAPVALUE = (((FICR->XOSC32MTRIM.SLOPE+56)*(CAPACITANCE*2-14)) + ((FICR->XOSC32MTRIM.OFFSET-8)<<4)+32)>>6

ЙПГжµД№«КЅЦРЈ¬CAPACITANCEОЄјДґжЖчXOSC32MCAPS.CAPVALUEµДЦµЈ¬FICR->XOSC32MTRIM.SLOPEєНFICR->XOSC32MTRIM.OFFSETОЄјДґжЖчXOSC32MTRIMЦРµДЦµЎЈCAPVALUE µДИЎЦµ·¶О§Ј¬јґДЪІїБЅёцµзИЭГїТ»ёцµзИЭЦµµДИЎЦµ·¶О§КЗ7pfµЅ20pfЈ¬ѕ«¶ИОЄ0.5pfЎЈ

ОТГЗїЙТФНЁ№э¶БИЎПа№ШµДјДґжЖчЦµЈ¬Аґ»сµГ№«КЅЦР±дБїµДЦµ

PS C:\Users\stli\Desktop> nrfjprog --memrd 0xff0c20

0x00FF0C20: FFFFFE01

їЙµГµЅЈє

FICR->XOSC32MTRIM.SLOP=1

FICR->XOSC32MTRIM.OFFSET=16

PS C:\Users\stli\Desktop> nrfjprog --memrd 0x500045c4

0x500045C4: 0000010C

їЙµГµЅЈє

XOSC32MCAPS.ENABLE=1,ґъ±нК№УГБЛДЪІїµзИЭЎЈ

CAPACITANCE=12

ґшИ빫ʽїЙТФµГµЅЈє

CAPVALUE=10pf

НЁ№эТФЙПСйЦ¤Ј¬ОТГЗЦЄµАРѕЖ¬іці§К±Ј¬ёЯЖµѕ§ХсДЪІїµзИЭКЗК№ДЬµДЈ¬ЗТГїТ»ёцµзИЭµДИЭЦµКЗ10pfЎЈ

3.ИзєОИҐРЮёДёЯЖµѕ§ХсДЪІїЖҐЕдµзИЭЦµЈї

NCSМṩБЛБЅёцKconfigЈ¬Н¬К±ЕдЦГТФПВБЅёцєкјґїЙЈє

CONFIG_SOC_HFXO_CAP_INTERNAL=y

CONFIG_SOC_HFXO_CAP_INT_VALUE_X2=14

CONFIG_SOC_HFXO_CAP_INT_VALUE_X2ЦёµДКЗДЪІїБЅёцµзИЭјУЖрАґµДЦµЈ¬јґИз№ыЛьµДЦµОЄ14ДЗГґГїТ»ёцµзИЭµДЦµОЄ7pfЈ¬Из№ыЛьµДЦµОЄ15ДЗГґГїТ»ёцµзИЭЦµОЄ7.5pfЎЈ

4.Из№ыТ»¶ЁТЄНв№ТБЅёцёЯЖµѕ§ХсµДНвІїµзИЭЈ¬ТІКЗУР·Ѕ·ЁµДЈє

CONFIG_SOC_HFXO_CAP_EXTERNAL=y

ХвСщѕНїЙТФ°СДЪІїµзИЭ¶ПїЄЈ¬ёДОЄК№УГНвІїµзИЭЎЈІ»№эТ»°гЗйїцПВІ»ЅЁТйК№УГНвІїµзИЭЈ¬ДЪІїµзИЭКЎК±КЎБ¦єОАЦ¶шІ»ОЄДШЈї

5.ИзєОµчКФёьёДµНЖµѕ§ХсµДДЪІїµзИЭЎЈ

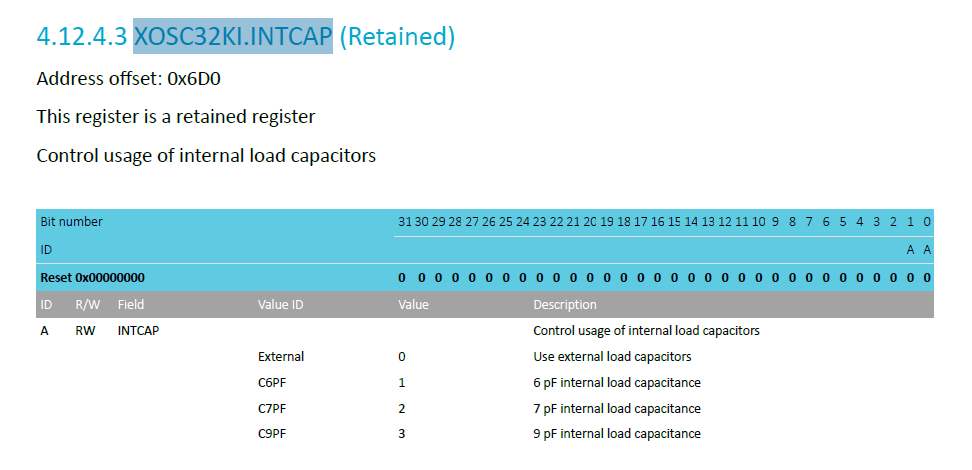

НЁ№эјДґжЖчXOSC32KI.INTCAPёьёДЈє

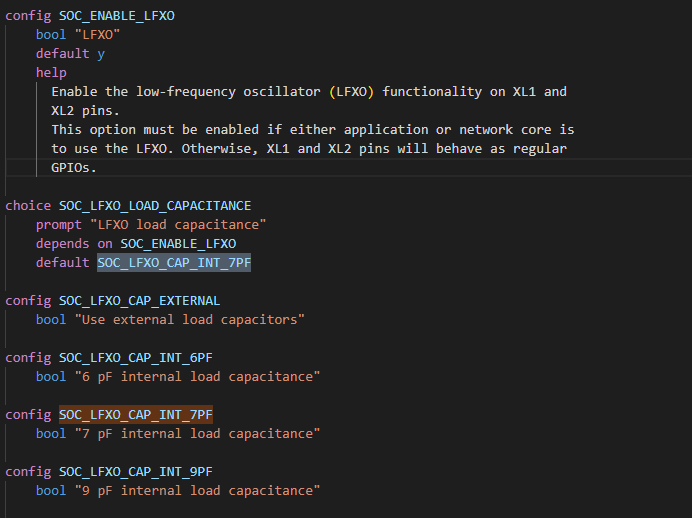

NCSЦР¶ФУ¦µДKconfigЈє

6.Из№ыРиТЄёьЅшТ»ІЅЅЪКЎBOMіЙ±ѕЈ¬Н¬К±І»ФЪєхВФОўµД№¦єДМбЙэЈ¬ЙхЦБїЙТФ°СНвІїµДµНЖµѕ§ХсТІКЎВФµфЈ¬ѕЯМеЕдЦГ·Ѕ·ЁИзПВЈє

CONFIG_CLOCK_CONTROL_NRF_K32SRC_RC=y

CONFIG_CLOCK_CONTROL_NRF_K32SRC_RC_CALIBRATION=y